- Behavioral Systemverilog Module For 4-to-1 Mux Video

- Behavioral Systemverilog Module For 4-to-1 Mux Price

Verilog MultiplexerMultiplexerWe will continue to learn more examples with multiplexer. A multiplexer selects one of severalinput signals and forwards the selected input into a single line.A single bit multiplexer will have one control line two inputs ( say X and Y) and one output ( say Z). When the conrolsis 0, X is connected to Z. When the Control is 1, Y is connected to Z.The figure below explains thisWe can extend this idea to increase the number of the control bits to 2. This 2 bit multiplexer will connect one of the 4inputs to the out put.We will now write verilog code for a single bit multiplexer.mux.v. We have used assignment statement that uses conditional operatorassign out = cntrl? In1: in2;The conditional operator is makes use of?

Its syntax is as followsConditional Expression? True expression: false expressionThe conditional expression is evaluated and and if it is true, the 'true expression' else 'false expression' is evaluated.Looking at the example above the cntrl is evaluated and if it is 1, the in1 is assigned to out else in2 is assigned to out.We will now add a test bench to confirm that the result is as expected. So here goes the test bench.mux2tb.v. As usual we will compile the program with following commandsC:iverilogbinsrcmuxiverilog -o output mux2.v mux2tb.vC:iverilogbinsrcmuxvvp output0 out=0,cntrl=0,in1=0,in2=01 out=0,cntrl=0,in1=1,in2=02 out=1,cntrl=0,in1=0,in2=13 out=1,cntrl=0,in1=1,in2=14 out=1,cntrl=1,in1=1,in2=15 out=0,cntrl=1,in1=0,in2=06 out=1,cntrl=1,in1=1,in2=07 out=0,cntrl=1,in1=0,in2=18 out=1,cntrl=1,in1=1,in2=1Exercise1. Extend the multiplexer with 2 control bits and 4 inputs.SolutionBefore looking at the solution, make sure you have given your efforts to solve it.

Here are the solution codes.

For this lab, instead of simulating a circuit in MultiSim and then physically building it using chips on a breadboard, we will build and simulate a circuit using SystemVerilog. As discussed in lecture a few weeks ago, SystemVerilog is a hardware description language (HDL) that allows hardware to be described at a higher abstraction level (focusing on function over structure) in a syntax that somewhat resembles C. Electronic design automation (EDA) tools simulate the functionality of the described circuit in order to allow verification and then synthesize the description into an actual gate- or transistor-level model. SystemVerilog is the HDL of choice for nearly all of the major microprocessor design companies, including several with design teams in Austin (e.g, Intel, AMD) who have hired Texas State students for internships in the past.

This lab is intended to give you the minimum SystemVerilog skills required for an internship interview with one of these teams. (We've snuck in a tiny bit of computer design, too). In this lab, you will design an 8-bit arithmetic logic unit (ALU) that implements 2's complement addition and subtraction using ripple-carry.

You will then implement a device, called the device under test (DUT), that incorporates this ALU and does the following:. Takes as input four 8-bit data values Takes as input a 5-bit opcode, which can be thought of as a machine instruction.

Each bit or pair of bits encodes an instruction to the device, as follows: o opcode4: A value of 0 means 'add', a value of 1 means 'subtract o opcode(3:2 This 2-bit value chooses the first data operand to the addition/subtraction, i.e. 2'b00 selects data0, 2'b01 selects datal, 2'b10 selects data2, and 2'b11 selects data3 opcode 1:0: This 2-bit value chooses the second data operand to the addition/subtraction, Le. 2'b00 selects data0, 2'b01 selects data1, etc. O.Based on the values of the opcode input, selects the two operand values from among the data inputs and provides them as input to the ALU along with a control bit specifying if the operation is an add or a subtract.

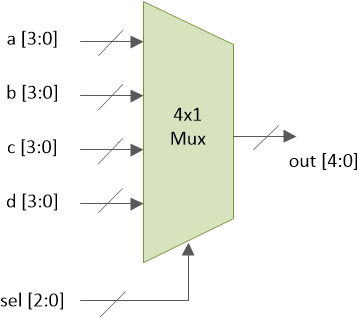

(Hint: you will need a 4:1 mux for each data operand, to do the selection). Outputs the 8-bit result from the addition/subtraction.Outputs a 1-bit value, overflow, that will be 1 if the operation overflowed and 0 otherwise. Lastly, you will verify your design using the provided testbench.sv file. The provided testbench contains both a stimulus generator, which provides testcases to the DUT, and a checker to verify that the DUT provides the correct result for each input testcase. Below is an overview diagram of what your DUT module should describe: dut data0l7:0) data17:0 data2 7:0 data37:0 result7:0 mux overflow 3:2: sel ALU mux 1:0: sel 4: subtract opcode4:0In order to ensure that it can be wired to my testbench module, I have provided a stub of the DUT module in design.sv. Do not change the input or output names in this module.

You will need to fill in the SystemVerilog description in module dut0 as well as define and instantiate several other modules. Below, I have provided brief descriptions and black-box diagrams of the other modules you must create. It's your job to figure out how to design the required internals of each module, to specify them in SystemVerilog, and to correctly connect them to implement the required functionality! (Feel free to name these auxiliary modules and their inputs/outputs anything you'd like; the diagrams below provide suggestions only).halfadder: This module should implement a half-adder in behavioral Verilog (i.e, continuous assignment statements or always comb blocks). Sum halfadder carry.fulladder: This module should implement a full-adder by instantiating two instances of your halfadder module (and adding a small amount of additional logic). Sum c out in.alu: This module should instantiate eight instances of your full adder module and chain the carries together to create a ripple-carry adder. When input 'subtract is 1, it should create the 2's complement of operand B before performing the addition.

(Note that this is very similar to HW3.10). It should also determine if overflow has occurred: recall that 2's complement overflow exists when the carry-in to the most-significant bit of the addition does not match the carry-out of the most-significant bit of the addition. Operand A7:0 operand BI7:0) subtract result7:0 alu overflow mux: This module should describe a 4:1 mux that selects its output from four 8-bit data inputs based on the value of the 2-bit select line, when sel#2.b00, out is set to in0; when sel 2.b01. Out is set to in1; etc. Refer to the SystemVerilog lecture slides for hints about how to describe a mux in behavioral SystemVerilog. Your solution will use an always.comb block and either if/else statements or a case statement. 7:0 in1 7:0 in2 7:0 n37:0 out 7:0 mux sell1:0Please note that all of your modules must use behavioral Verilog, i.e.

You may not use any of SystemVerilog's structural gate primitives! This means that if you need AND functionality, you should have something like 'assign x-a &b'or 'alwayscomb begin x-a & b end' NOT 'and g1(x, a, b)'. While Verilog does provide structural gate models, real-world design is done almost entirely in behavioral Verilog because it provides designers a more useful abstraction level. Pre-Laboratory Component: It is hypothetically possible to do this entire lab before you walk into your lab section, demo immediately, and go home early and you are welcome to do so! However, the following must be complete when you walk into lab 1.

One member of each lab benchgrou have an ED gro om istered to email address. Dothis mediately and confirm ou carilog in (From n In' upperr th emVefilo go andthake sueyou understand s or send ll ot the SystemVerilog snippets on the slides! (If you d her an ema 3.

Review my provided testbench.sv code and be able to describe what it does. Be able to explain the operation of a 4:1 mux. On paper, draw the internals of the fulladder and alu modules. You should have a diagram showing the additional gate(s) and connections needed to build a full-adder out of two half adders, and a second diagram showing how to build an 8-bit ripple-carry adder/subtracter out of 8 full-adders plus additional gates, and what's connected to what. Cobb fiesta st ots maps. The second diagranm should also have a gate used to detect overflow.

(Hint: overflow exists when the carry-in to the MSB does not equal the carry-out; what gate can tell us if two bits are not equal?) Feel free to start writing the SystemVerilog (and testing it in EDAPlayground.com) for any/all of the modules before you come to lab, but the above must be done when lab begins! Laboratory Component: In lab, you will use EDAPlayground.com to implement the device described above.

All of your code should go in design.sv. Paste my provided design.sv stub into the righthand window in EDAPlayground and paste my provided testbench.sv into the lefthand window.

Choose 'Synopsys VCS' under 'Tools & Simulators,' and check the checkbox for 'Open EPWave after run.' Hit 'Save often. 'Run' in the upper left will attempt to compile your model and run it in my testbench. My testbench module is self-checking and will report either PASSED or FAILED Get more help from Chegg.

Due to recent changes by Oracle, java applets have become difficult to run in the browser. To mitigate the troubles, Oracle has provided the following websites to help users troubleshoot: and after following the above instructions, loading applets may still show warning concerning “unsigned application” and “unknown publisher”. For Teahlab in particular, these warnings are due to the fact that we have opted not to pay a third party such as Verisign to sign our applets. Any warning that comes up when you try to run our applets should emphasize that our applets will always run with “limited access”, which is Oracle’s way of letting you know that teahlab doesn’t do anything on your computer except running the circuits you see: in other words, our applets are safe to run.Sincerely,The Teahlab Team. Your browser does not support iframes.Structure:- From a basic gates perspective, a 4-to-1 Mux is- constituted of four 3-input AND gates, three OR gates,- and two Inverters. When we speak of structural design- in VHDL, we mean precisely the description a circuit- by presenting its constituent components and- interconnecting wires.

The following VHDL program is a- structural design of the 4-to-1 multiplexer. As such- the circuit is designed in two stages:- In stage one we define the basic entities:- AND, OR, NOT.- In stage two we use the basic entities to construct- the Mux.- One of the advantages of structural designs is that- from the VHDL program you can tell what the physical- circuit looks like.- It is very important to learn structural design (RTL)- strategies because as your assignments become larger- and larger, knowledge of register transfer level (RTL)- design strategies become indispensable.

I need create 8.1 multiplexer by 2-1 multiplexer.At this time, my code can work. However, the output is incorrect.And the wires O0.O1,O2,O3 can work correctly.When the 2-1 multiplexer read the selector 1 and 2, it does not change.The output is between I0 AND I1.Can you help me with the problem? I believe, assign statement in the MUX21 is not proper.You have 2 options to rectify it.1st OptionYou can use ternary operator (which is more preferable, as per my opinion) assign o = (sel)?

Verilog Design:Different ways to code Verilog: A Multiplexer exampleThere are different ways to design a circuit in Verilog. In this tutorialI have used seven different ways to implement a 4 to 1 MUX.

After synthesizing,five of them gave same RTL level circuit in Xilinx Project navigator.Let us start with a block diagram of multiplexer.Example IIf select is 0, output q will be d0; if select is 1, q will be d1; ifselect is 2, q will be d2 and if select is 3, q will be d3. This logiccan be implemented using Verilog code as follows. // Verilog code forMultiplexer implementation using assign// File name: mux1.v// by Harsha Perla for//// Available atmodule mux1 (select, d,q );input 1: 0 select;input 3: 0 d;output q;wireq;wire 1: 0 select;wire 3: 0 d;assign q =d select ;endmoduledeclaration ' input 1: 0 select;' specifiesselect as port of 2 bits, with MSB select1 and LSB select0. All the portsare declared as arrays because all the input signals must be declared as wiresand left side of continuous statements should be wire. Actually, ports arewire by default and we need not declare it.

But it is better to declare forour convenience.When select is 00, q will be assigned d0, when select is 01, q will be assignedd1 and so on. To test this, use following testbench. It generates a truthtable with all possible values in the input and select. // Verilog testbench for 4 to 1 Multiplexer // by Harsha Perla for // Comments to: [email protected] // Available at module muxtb; reg 3: 0 d; reg 1: 0 select; wire q; integer i;mux1 mymux ( select, d, q ); initial begin # 1 $monitor ( 'd =%b', d, ' select = ', select, ' q = ', q ); for ( i = 0; i. // Verilog code for Multiplexer implementation using always block.

// by Harsha Perla for // [email protected] // Available at module mux 2( select, d, q ); input 1: 0 select; input 3: 0 d; output q; reg q; wire 1: 0 select; wire 3: 0 d; always @(d or select )q = d select ; endmoduleUse the same testbench as previous one for this code. Change mux1 mymuxby mux2 mymux.Example IIIThis example uses if statement of Verilog. Herealso q is declared as reg and other signals as wire. This example alsouses always block with the same sensitivity list. You can understand thiscode very easily. // Verilog code for Multiplexer implementation using if statement.

// by Harsha Perla for // [email protected] // Available at module mux3 ( select, d, q ); input 1: 0 select; input 3: 0 d; output q; reg q; wire 1: 0 select; wire 3: 0 d; always @( select or d ) begin if ( select 0 )q = d 0 ; if ( select 1 )q = d 1 ; if ( select 2 )q = d 2 ; if ( select 3 )q = d 3 ; end endmoduleActually this example (next one also) has more code to write. But ifselect and input signals are having separate name instead of packed arrayslike d1, d2, select1. This code is more easy to understand and very usefulif inputs are coming from different sources.Example IVNext example is also similar one. Here, case statement is used. Casestatement switches the execution of the code to corresponding blockdepending on the value of the parameter passed.

// Verilog code for Multiplexer implementation using case statement. // by Harsha Perla for // [email protected] // Available at module mux4 ( select, d, q ); input 1: 0 select; input 3: 0 d; output q; reg q; wire 1: 0 select; wire 3: 0 d; always @( select or d ) begin case ( select ) 0: q = d 0 ; 1: q = d 1 ; 2: q = d 2 ; 3: q = d 3 ; endcase end endmoduleExample VThis example uses nested conditional statement. Meaning of the assignstatement in the following code is 'If select = 0, q = d0, else ifselect is 1 q = d1. Else if select is 2 q = d2, else q = d3. We canuse conditional statement inside always block also. // Verilog code for Multiplexer implementation using conditional statement. // by Harsha Perla for // [email protected] // Available at module mux 5( select, d, q ); input 1: 0 select; input 3: 0 d; output q; wire q; wire 1: 0 select; wire 3: 0 d; assign q = ( select 0 )?

D 0 : ( select 1 )? D 1 : ( select 2 )? D 2 : d 3 ; endmoduleAll the examples till now uses behavioral style of coding. Next example isdata flow style of code.Example VIIf we write an expression for 4 to 1 multiplexer, we can convert theexpression in to code. Consider the expression bellow:q = (select0.

Select1.d0) + ( select0. Select1.d1) + ( select0.select1.d2) + ( select0.select1.d3 )You can write a truth table to verify the equation. Now we can write acode using Verilog for this equation as follows.

Behavioral Systemverilog Module For 4-to-1 Mux Video

We can also use assignstatement instead of writing always block. // Verilog code for Multiplexer implementation in dataflow level. // by Harsha Perla for // [email protected] // Available at module mux 6( select, d, q ); input 1: 0 select; input 3: 0 d; output q; reg q; wire 1: 0 select; wire 3: 0 d; always @( select or d ) beginq = ( select 0 & select 1 & d 0 ) ( select 0 & select 1 & d 1 ) ( select 0 & select 1 & d 2 ) ( select 0 & select 1 & d 3 ); end endmoduleExample VIIThis example is gate level implementation of themultiplexer. All basic gates are declared in Verilog. We can instantiatethem to get a gate level circuit.

Behavioral Systemverilog Module For 4-to-1 Mux Price

Let us draw the diagram of multiplexerfirst.Now, convert the circuit in to code. Instantiate2 NOT gates, four AND gates and one OR gate as in the diagram. All theoutputs from the gates should be wire. Hence code contains all the signalsas wires. // Verilog code for Mux implementation using instantiating gates.